The Sample and Hold block acquires the input at the signal port whenever it receives a trigger event at the trigger port (marked by ). The block then holds the output at the acquired input value until the next triggering event occurs.

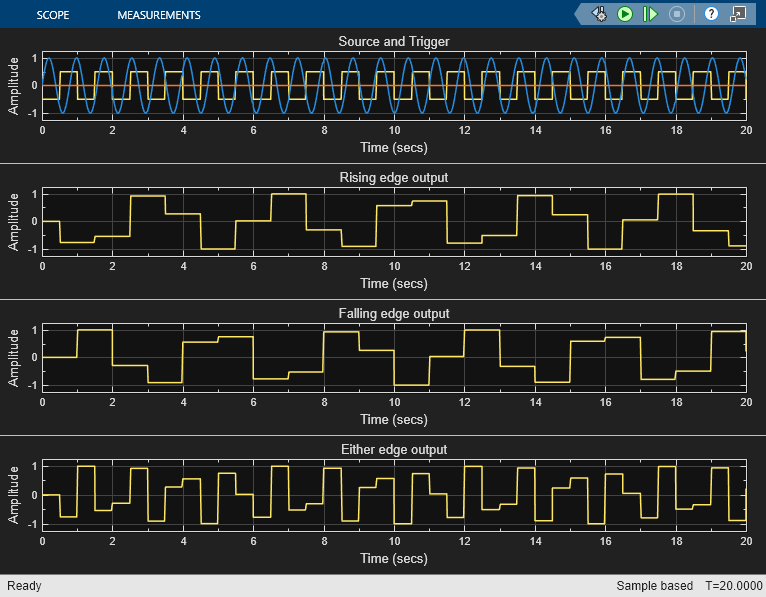

Shows the effect of different trigger events on output of the Sample and Hold block.

The signal port can accept data in the form of a scalar, vector, or matrix.

This port is named In when you select the Latch (buffer) input parameter.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

The trigger input must be a sample-based scalar with sample rate equal to the input frame rate at the signal port. You specify the trigger event using the Trigger type parameter.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Sample and hold output, returned as a scalar, vector, or a matrix. The block acquires input at the signal port whenever it receives a trigger event at the trigger port. The block then holds the acquired data until the next triggering event occurs.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

The type of event that triggers the block to acquire the input signal:

Specify the block's output before the first trigger event using the Initial condition parameter. When the acquired input is an M-by-N matrix, the Initial condition can be an M-by-N matrix or a scalar repeated across all elements of the matrix. When the input is a length-M unoriented vector, the Initial condition can be a length-M row or column vector, or a scalar to be repeated across all elements of the vector.

If you select the Latch (buffer) input check box, the block outputs the value of the input from the previous time step until the next triggering event occurs. To use this block in a loop, select this check box.

Data Types

Boolean | double | fixed point | integer | single

Direct Feedthrough

Multidimensional Signals

Variable-Size Signals

Zero-Crossing Detection

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

HDL code for the Sample and Hold block is generated as a Triggered Subsystem . Similar restrictions apply to both blocks. See Using Triggered Subsystems for HDL Code Generation (HDL Coder) .

HDL Block PropertiesFor HDL block property descriptions, see HDL Block Properties: General (HDL Coder) .

Best PracticesWhen using the Sample and Hold block in models targeted for HDL code generation, consider the following:

The Sample and Hold block must meet the following conditions:

Introduced before R2006a